# Czech Technical University in Prague

Faculty of Electrical Engineering

Department of Measurement

Master's thesis

Profibus Analyzer – Communication Driver and Firmware Update

Author: Bc. Daniel Kubeš Supervisor: RNDr. Petr Štěpán, Ph.D.

# MASTER'S THESIS ASSIGNMENT

## I. Personal and study details

| Student's name:      | Kubeš Daniel                      | Personal ID number: | 420144 |

|----------------------|-----------------------------------|---------------------|--------|

| Faculty / Institute: | Faculty of Electrical Engineering |                     |        |

| Department / Institu | ite: Department of Measurement    |                     |        |

| Study program:       | Cybernetics and Robotics          |                     |        |

| Branch of study:     | Sensors and Instrumentation       |                     |        |

#### II. Master's thesis details

Master's thesis title in English:

Profibus Analyzer - Communication Driver and Firmware Update

Master's thesis title in Czech:

#### Modifikace programového vybavení komunikačního zařízení Profibus Analyzer

#### Guidelines:

- 1. Familiarize with the Siemens internal project Profibus Analyzer and RT Linux kernel system.

- 2. Port U-Boot & Linux (based on version 4.9.28) to Profibus Analyzer board, which is based on TI SITARA MCU.

- 3. Design & Implement the Linux kernel driver for communication with FPGA based on implemented parallel interface, adapt the existing application of Profibus Analyzer if necessary.

- 4. Design & Implement the firmware update strategy for Profibus Analyzer which includes the FPGA firmware, Linux kernel driver and Application.

- 5. Verify and document the solution.

Bibliography / sources:

Name and workplace of master's thesis supervisor:

#### RNDr. Petr Štěpán, Ph.D., Multi-robot Systems, FEE

Name and workplace of second master's thesis supervisor or consultant:

Date of master's thesis assignment: 09.10.2017

Deadline for master's thesis submission: 25.05.2018

Assignment valid until: by the end of summer semester 2018/2019

RNDr. Petr Štěpán, Ph.D.

Head of department's signature

prof. Ing. Pavel Ripka, CSc.

Supervisor's signature

Dean's signature

#### III. Assignment receipt

The student acknowledges that the master's thesis is an individual work. The student must produce his thesis without the assistance of others, with the exception of provided consultations. Within the master's thesis, the author must state the names of consultants and include a list of references.

Date of assignment receipt

Student's signature

# Author statement for undergraduate thesis

I declare that the presented work was developed independently and that I have listed all sources of information used within it in accordance with the methodical instructions for observing the ethical principles in the preparation of university theses.

Prague, date: .....

Signature: .....

## Acknowledgement

I would like to express my gratitude to my supervisor RNDr. Petr Štěpán, Ph.D. for his supportive guidance, his useful advice and comments during the writing.

I would also like to thank my family and my girlfriend who supported me during the whole time of my studies.

Last but not least, I would like to thank my colleagues from the Siemens for the support with the practical part of the thesis.

## Abstrakt

Tato diplomová práce se zabývá vývojem firmwaru pro zařízení Profibus Analyzer od firmy Siemens. Zařízení bude možné využít pro analýzu dvou kanálů Profibus DP a jednoho kanálu PA v jedné časové doméně, což je nezbytně nutné pro precizní analýzu Profibus zařízení, které využívá redundatní komunikační kanál.

V práci je popsán vývoj komunikačního řetězce sloužícího k přenosu dat z FPGA, které zpracovává data z Profibus kanálů, do PC aplikace. Jeho základem je procesor Sitara, na kterém běží operační systém Linux. Zmíněný komunikační řetězec obsahuje modul linuxového jádra, který zajišťuje přenos dat z FPGA do paměti procesoru, real-time aplikaci, která komunikuje s kontrolní PC aplikací a předává ji naměřená data z FPGA a nakonec dynamickou knihovnu (.dll) pro zapouzdření komunikace mezi Profibus Analyzerem a počítačem, která bude využita pro kontrolní GUI aplikaci.

## Klíčová slova

Profibus, Profibus DP, Profibus PA, Fieldbus, Analyzátor, FPGA, Sitara procesor, AM335x, TI, Linux, RT patch, Kernel modul, Real Time aplikace, Server-klient, Siemens

## Abstract

This diploma thesis focuses on the firmware development for the Profibus Analyzer device made by the Siemens company. It will be possible to use this device to analyze two Profibus DP channels and one PA channel in the same time domain, which is necessary to achieve a precise analysis of the Profibus device, which uses a redundant communication channel.

The thesis describes the development of the communication stack, which ensures the data transfer from the FPGA (that processes the Profibus channels data) to the PC application. The communication stack is based on the Sitara processor running the Linux OS. This stack contains Linux kernel module, the real-time application and the Dynamic Link Library. Linux kernel module is responsible for the data transfer from the FPGA to the processor memory, the real-time application communicates with the control PC application and forwards the FPGA data to the PC and the Dynamic Link Library encapsulates the whole communication between the PC and the Profibus Analyzer to be used by the control GUI application.

## Keywords

Profibus, Profibus DP, Profibus PA, Fieldbus, Analyzer, FPGA, Sitara processor, AM335x, TI, Linux, RT patch, Kernel module, Real Time application, Server-client, Siemens

# Contents

| 1        | Inti | roduction                                                                                                   | 1  |  |  |  |

|----------|------|-------------------------------------------------------------------------------------------------------------|----|--|--|--|

| <b>2</b> | Pro  | Profibus                                                                                                    |    |  |  |  |

|          | 2.1  | History                                                                                                     | 2  |  |  |  |

|          | 2.2  | Present time                                                                                                | 2  |  |  |  |

|          | 2.3  | Topology                                                                                                    | 2  |  |  |  |

|          | 2.4  | ISO/OSI                                                                                                     | 3  |  |  |  |

|          |      | 2.4.1 Application layer                                                                                     | 3  |  |  |  |

|          |      | 2.4.2 Link layer                                                                                            | 4  |  |  |  |

|          |      | 2.4.3 Physical layer                                                                                        | 4  |  |  |  |

|          | 2.5  | Protocols                                                                                                   | 4  |  |  |  |

|          |      | 2.5.1 Profibus DP                                                                                           | 5  |  |  |  |

|          |      | 2.5.2 ProfibusPA                                                                                            | 5  |  |  |  |

|          | 2.6  | Telegrams                                                                                                   | 5  |  |  |  |

|          |      | 2.6.1 Transfer type                                                                                         | 5  |  |  |  |

|          |      | 2.6.2 Characters                                                                                            | 5  |  |  |  |

|          |      | 2.6.3 Telegram structure                                                                                    | 5  |  |  |  |

|          |      |                                                                                                             |    |  |  |  |

| 3        | Pro  | ofibus Analyzer device overview                                                                             | 6  |  |  |  |

|          | 3.1  | Hardware                                                                                                    | 7  |  |  |  |

|          |      | 3.1.1 Sitara processor                                                                                      | 8  |  |  |  |

|          | 3.2  | Software                                                                                                    | 9  |  |  |  |

|          | 3.3  | Profibus Analyzer use cases                                                                                 | 9  |  |  |  |

| 4        | Lin  | ux                                                                                                          | 12 |  |  |  |

|          | 4.1  | Introduction                                                                                                | 12 |  |  |  |

|          | 4.2  | History                                                                                                     | 12 |  |  |  |

|          | 4.3  | Kernel architecture                                                                                         | 13 |  |  |  |

|          | 4.4  | Real Time Preemptible Patch                                                                                 | 13 |  |  |  |

|          |      | 4.4.1 Real-Time Operating System (RTOS)                                                                     | 13 |  |  |  |

|          |      | 4.4.2       Real-Time Preempt Patch for Linux kernel                                                        | 14 |  |  |  |

|          | 4.5  | Kernel module and device tree basics                                                                        | 14 |  |  |  |

|          | 4.0  | 4.5.1 Kernel module                                                                                         | 14 |  |  |  |

|          |      |                                                                                                             |    |  |  |  |

|          |      | 4.5.2 Device tree $\ldots$ | 15 |  |  |  |

| <b>5</b> | $\mathbf{Lin}$ | ux inst | allation on Profibus Analyzer hardware | 15 |

|----------|----------------|---------|----------------------------------------|----|

|          | 5.1            | Proces  | sor SDK                                | 15 |

|          | 5.2            | Bootin  | g procedure                            | 16 |

|          |                | 5.2.1   | ROM (primary) bootloader $\ldots$      | 16 |

|          |                | 5.2.2   | Secondary bootloader                   | 17 |

|          |                | 5.2.3   | U-boot                                 | 17 |

|          |                | 5.2.4   | Kernel                                 | 18 |

|          | 5.3            | U-boo   | t porting                              | 18 |

|          |                | 5.3.1   | Configuration                          | 18 |

|          |                | 5.3.2   | Board init                             | 18 |

|          |                | 5.3.3   | Card Detect Signal                     | 19 |

|          | 5.4            | Linux   | kernel porting                         | 19 |

|          |                | 5.4.1   | Configuration                          | 19 |

|          |                | 5.4.2   | Device tree                            | 19 |

| 6        | Pro            | fibus A | Analyzer driver                        | 20 |

|          | 6.1            | Driver  | design                                 | 20 |

|          |                | 6.1.1   | Initialization/deinitialization        | 20 |

|          |                | 6.1.2   | Control interface                      | 21 |

|          |                | 6.1.3   | Functionality                          | 24 |

|          | 6.2            | Driver  | implementation                         | 25 |

|          |                | 6.2.1   | Source code structure                  | 25 |

|          |                | 6.2.2   | Data transfer functionality            | 26 |

|          |                | 6.2.3   | Control interface to the user-space    | 27 |

|          |                | 6.2.4   | Device tree                            | 29 |

|          | 6.3            | Examp   | ble of driver usage                    | 31 |

|          | 6.4            | _       | tion of driver implementation          | 32 |

|          |                | 6.4.1   | FPGA test design                       | 32 |

|          |                | 6.4.2   | User-space test application design     | 32 |

| 7        | Pro            | fibus A | Analyzer Application                   | 33 |

|          | 7.1            | Applic  | ation design                           | 33 |

|          |                | 7.1.1   | Initialization                         | 33 |

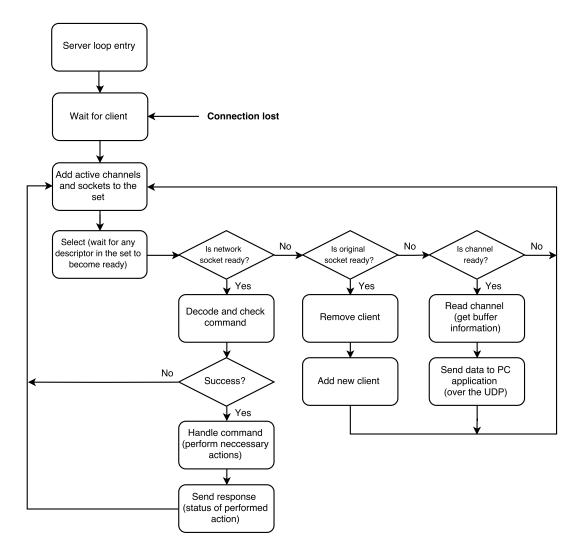

|          |                | 7.1.2   | Server/control loop                    | 34 |

|          | 7.2            |         | ation implementation                   | 35 |

|          | =              | 7.2.1   | Code structure                         | 35 |

|          |                | 7.2.2   | Network configuration                  | 36 |

|          |                | 7.2.3   | Server behavior                        | 36 |

|          |                | -       |                                        |    |

|   |                   | 7.2.4                                               | Traces                                      | 37                                                                                 |

|---|-------------------|-----------------------------------------------------|---------------------------------------------|------------------------------------------------------------------------------------|

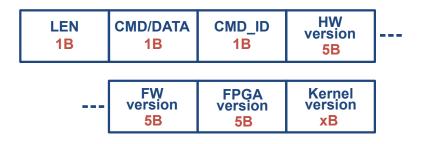

|   |                   | 7.2.5                                               | Communication protocol with PC application  | 37                                                                                 |

|   | 7.3               | FPGA                                                |                                             | 41                                                                                 |

|   |                   | 7.3.1                                               | Design                                      | 41                                                                                 |

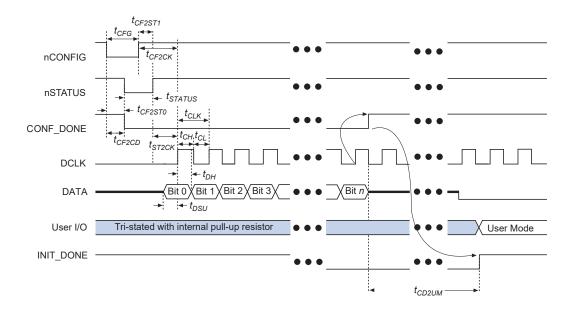

|   |                   | 7.3.2                                               | Bitstream loading                           | 42                                                                                 |

|   | 7.4               | Valida                                              | tion of application implementation          | 43                                                                                 |

|   |                   | 7.4.1                                               | PC test application design                  | 43                                                                                 |

|   | 7.5               | Firmw                                               | are update strategy                         | 44                                                                                 |

|   |                   | 7.5.1                                               | Design                                      | 44                                                                                 |

|   |                   | 7.5.2                                               | Update protocol                             | 44                                                                                 |

|   |                   | 7.5.3                                               | Archive format                              | 47                                                                                 |

|   |                   | 7.5.4                                               | Usage                                       | 48                                                                                 |

| 8 | D                 |                                                     |                                             |                                                                                    |

|   | Pro               | fibus A                                             | Analyzer DLL                                | <b>49</b>                                                                          |

|   | <b>Pro</b><br>8.1 |                                                     | Analyzer DLL         nic Link Library (DLL) | <b>49</b><br>49                                                                    |

|   |                   |                                                     |                                             |                                                                                    |

|   |                   | Dynar                                               | nic Link Library (DLL)                      | 49                                                                                 |

|   |                   | Dynar<br>8.1.1<br>8.1.2                             | nic Link Library (DLL)                      | 49<br>49                                                                           |

|   | 8.1               | Dynar<br>8.1.1<br>8.1.2                             | nic Link Library (DLL)                      | 49<br>49<br>49                                                                     |

|   | 8.1               | Dynar<br>8.1.1<br>8.1.2<br>Profib                   | nic Link Library (DLL)                      | 49<br>49<br>49<br>51                                                               |

|   | 8.1               | Dynar<br>8.1.1<br>8.1.2<br>Profib<br>8.2.1<br>8.2.2 | nic Link Library (DLL)                      | <ol> <li>49</li> <li>49</li> <li>49</li> <li>51</li> <li>51</li> </ol>             |

|   | 8.1<br>8.2        | Dynar<br>8.1.1<br>8.1.2<br>Profib<br>8.2.1<br>8.2.2 | nic Link Library (DLL)                      | <ol> <li>49</li> <li>49</li> <li>49</li> <li>51</li> <li>51</li> <li>52</li> </ol> |

#### 9 Conclusion

$\mathbf{54}$

# 1 Introduction

Nowadays, when a manufacturing process becomes more automated, new technologies are introduced almost on a daily basis and a human becomes an assistant of a robot, the Industry 4.0 concept was introduced (the name was first used in 2011 at the Hannover Fair). The key idea is to make communication among whole range of devices possible so they could cooperate more effectively - from the industrial machines, actuators and sensors to the IoT (Internet of Things). This means that a complex computer networks have to be used in factories. One family of these networks is called Fieldbus (standardized as IEC 61158).

Fieldbus finds its place everywhere in the factory, where instruments (such as PLCs to sensors or actuators) have to be connected together and perform real-time communication. An old version of Fieldbus standard contained eight different protocol sets (called "types"), but the current version from 2008 reorganized types into Communication Profile Families (CPFs). [1]

PROFIBUS (Process Field Bus) is one of CPFs and therefore also a family member of the Fieldbus standard. It is used in many applications in a field of factory automation and in a safety applications like chemical plants or power stations as well. For the safety applications, redundancy concepts were introduced by specification (only vendor-specific redundancy concepts were available earlier) to achieve required higher safety level. There are few kinds of redundancy defined in Profibus - Master redundancy (the control system is redundant), Media redundancy (uses redundant media for transmission), Coupler/gateway redundancy (where if one fails, the other one will take care about coupling), Ring redundancy (which is a combination of few redundancies and therefore more complex) and a Slave redundancy (where field devices are redundant). [2]

For every communication technology it is necessary to provide some diagnostic tools for analysis, data capture and statistics measurement. If we take a look at a situation on a market, there are few solutions for Profibus channel diagnostic - for example Procentec Analyzer or Softing Analyzer. They share some common features such as USB interface, a scan of topology or bar graphs of measured data and both devices provide PC application. Procentec provides support for Profibus DP or PA (one at a time) and Softing provides support for both Profibus DP and PA at the same time. But these solutions are not sufficient enough in the case when any redundancy feature of Profibus is used. There is actually no suitable solution for this problem at all, which would be able to analyze Profibus Slave Redundancy (2x DP channel) and a PA channel in one time domain. [4]

A new solution for Profibus analysis that will be able to analyze not just a single Profibus channel, but also applications of slave redundancy in one time domain is currently being developed by Corporate Technology department of Siemens Company. This solution will be called a Profibus Analyzer in this paper.

The aim of this thesis is to develop a firmware part of Profibus Analyzer running on the Sitara processor (which includes the kernel platform driver and the Linux application) and to design a communication protocol for control application running on PC. However, this thesis does not contain the development of hardware and FPGA application, which have been already prepared. The control PC application (GUI) is also not contained in this thesis. It is important to distinguish between two terms, which will occur in the thesis - Profibus Analyzer Application is a firmware part of the thesis, however control PC application is not a part of the thesis, but it will be mentioned several times also.

## 2 Profibus

In this chapter, only the main features Profibus technology are mentioned, because it is impossible to put the whole description of this technology into this work.

As mentioned in the Section 1, Profibus (Process Field Bus) is a part of the Fieldbus standard and it is widely used in industrial automation system networks.

#### 2.1 History

Profibus was developed in Germany in the late 1980s by several companies such as Bosch, Siemens and Klöckner & Möller in cooperation with German universities.

The 1990s were quite an interesting historical period from the technological point of view. It was called The German-French Fieldbus War. The experts realized that the ensuring of compatibility would become too difficult with many different protocols, so they finally decided to create one standard to cover all used protocols. They tried to combine German Profibus, French FIP (Factory Instrumentation Protocol) and subsequently another ones, but the approaches of these systems were different and it took a lot of effort to combine them in the best possible way and a lot of compromises had to be made. During the process (which took more than 8 years), the attempt to combine these technologies was called sarcastically "The two-headed monster" due to different approaches. First success, and for the long time the last one, came in the 1993, when the physical layer definition was released by IEC 61158-2 and has been widely used since. [2]

Above the physical layer, the standardization did not work properly. The result was always too complex, complicated to maintain, too expensive and therefore almost useless. Because the attempts took so much time, Fieldbus systems were already on the market and were already used in industrial automation and nobody wanted to abandon his product because of the new standard. Therefore a completely new way was introduced - not to combine the Fieldbus systems to a single technology, but to make a standard accommodating all Fieldbus systems as it was. The compromise was finally made in 1999 when standard (IEC 61158) accomodating eight Fieldbus systems was released by Fieldbus Foundation. [2]

## 2.2 Present time

Nowadays, Profibus is no longer used for new projects in such amount as at the turn of the millennium, because more advanced technologies such as Profinet were developed. Nevertheless, there are still millions of devices, which have to be maintained and supported for the whole lifecycle. Moreover, it is used also in projects where the potential redesign to more advanced networks would cost a lot more money and also time than preserving a Profibus communication (for example systems in a nuclear power plant). For that reasons new devices are still developed and Profibus is still well maintained.

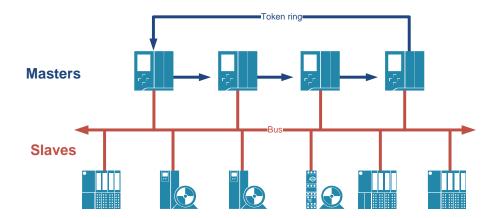

## 2.3 Topology

Profibus uses a bus topology. In case of a multi-master network, the Token passing method is used for media access control - a token is passed among all master devices (active nodes) in a ring - only a master that is in possession of the token can transmit. The other masters have to wait until they get the token to be able to start the communication and the slave devices (passive node) have to wait till the master with a token starts the communication with them (by polling). Just a simple master/slave communication scheme is used in the case of a single master. [3]

Figure 1: Bus topology

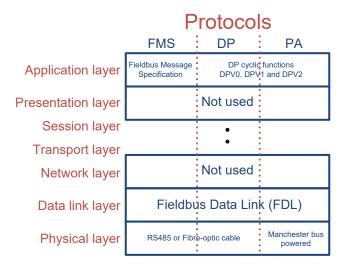

#### 2.4 ISO/OSI

ISO/OSI reference model is a result of attempts to standardize the computer networks - it divides the communication procedure into seven different layers, which solve different kinds of problems of communication procedure.

Profibus defines just three layers of ISO/OSI reference model - Application layer, Data Link layer and Physical layer. The other four layers are not used by the Fieldbus standard. [3]

Figure 2: Profibus ISO/OSI model

#### 2.4.1 Application layer

This layer provides services for final applications and hides the layers below for the user. To be able to work in so many different areas with a different desired performance, the Application layer provides three performance levels of DP cyclic functions:

- DP-V0 provides the basic functionality, which includes the cyclic communication and some part of diagnostics (for example indication of short-circuited output).

- DP-V1 is an extension of the previous DP-V0. The acyclic communication is added, which enables the use of alarms, parametrization and online access to the bus using debugging tools.

• DP-V2 is an extension of the previous DP-V1 (and therefore contains also DP-V0 functionality). It allows slaves to communicate with another slave, cycle synchronization and time stamping.

Another component of the Application layer is the Profibus Fieldbus Message Specification. It is the initial form of Profibus protocol that provides complex message structure. It is used for communication between two masters acyclically (peer-to-peer), as it was intended to allow coordination between different PLCs. Nowadays it seems to be fading away, because the Profibus DP in combination with FDL can replace this old feature. [2]

#### 2.4.2 Link layer

This layer is called Fieldbus Data Link (FDL) layer in Profibus standard. It is responsible for media access control, which is described above in the Subsection 2.3.

The most important point is that this layer, this media access method in more detail, makes Profibus a deterministic network and therefore it can guarantee that every single device will be accessed within a fixed time.

FDL is also responsible for the autodetecting of a bus speed which is slave connected to (so the speed of the slave is configured automatically). Another feature of FDL is that it provides a network scan - FDL request is periodically sent by the master to ensure that the slave is still present on the bus and is able to respond. To ensure at least a minimal level of security, even parity bit is added to each byte with a start and a stop bit by FDL.

#### 2.4.3 Physical layer

The Physical layer, how the name tells us, takes care of the physical transfer of information to another device bit by bit. Profibus standard provides a few different ways how the transmission technology can be implemented:

- Metallic cable is based on a well-known standard RS-485. It uses a twisted copper cable with a pair of conductors to avoid interferences in noisy environments (which is not a rare situation in the industry). A logical level is determined by the voltage difference between the pair of conductors, therefore devices can have a different power supply with different ground offsets. The maximal data transmission rate is 12 Mbps. The speed is determined by network complexity and a cable length, which can range from 100 m to 1 km (without repetitors). Metallic cable is the most common Physical layer.

- Fiber-optic cable is even better in noisy environments than RS-485 variant, because no electromagnetic noise can interfere with transmission in the optic cable. High transmission speeds can be reached for larger distances.

- Intrinsically safe transmission is defined for Profibus PA (described below). It is a standard for hazardous environments, which uses a current loop (industry standard of 4-20 mA). It has the fixed data rate at 31.25 kbps.

## 2.5 Protocols

There are several versions of Profibus protocols - Fieldbus Message Specification (FMS), Decentralized Peripherals (DP) and Process Automation (PA). Protocols are defined by a complete set of ISO/OSI layers features as indicated in the figure 2.

#### 2.5.1 Profibus DP

Profibus Decentralized Peripherals is used when a central controller wants to communicate with actuators or sensors, but it can also be used to communicate with other controller and therefore makes internetworking of several controllers possible (multi-master devices).

This protocol provides both cyclical and acyclical communication and defines rules for them. The Application layer uses DP cyclic functions, the Data Link layer uses FDL and the Physical layer uses metalic or fibre-optic cable.[14]

#### 2.5.2 ProfibusPA

Profibus Process Automation has almost the same features as DP except the Physical layer, where the intrinsically safe transmission is used. It can be used for the control measuring devices in process engineering and it is suitable for explosion or hazardous areas. Another feature is that it supplies the end devices via bus cable. [3]

PA network always has to be a part of a DP network, because it cannot exist without a DP master. [3]

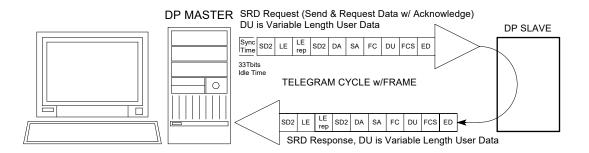

#### 2.6 Telegrams

The data and messages are transferred in the Data Link layer using the Profibus telegrams. [14]

#### 2.6.1 Transfer type

There are two ways of data transmission defined by the Link layer - SRD (Send and Request Data with acknowledge) and SDN (Send Data with No acknowledge) for Profibus DP.

As the names tell us, if SRD type is used, the device sends data and at the same cycle it expects some response with the data. This way is therefore really effective and fast, because the communication is performed just in one telegram cycle.

The SDN type is used whenever the message should be sent to the group of devices or to all of the devices (broadcast). The acknowledge is not expected on the sender side.

Just note here that there is another type called SDA (Send Data with Acknowledge) that is used for Profibus TMS. The acknowledge is expected to be received by the sender.

#### 2.6.2 Characters

The telegrams are created by characters - the following description applies to every byte transfer over Profibus.

Each character length is strictly fixed to 11 bits, which contains a single byte of data, start bit, stop bit and parity (even). Bits are transferred using the NRZ (Non-Return to Zero) code with LSB (Least Significant Bit) first (in case of transfer of word it is used Big-Endian format). The idle state is logic one, when the start bit is transmitted, it pulls the line down. This format of transfer is known for example from the RS232 standard.

#### 2.6.3 Telegram structure

The telegram contains several parts (or fields), all of them can be found in the list below according to the position in the telegram, from the beginning to the end (the size of each field in bytes can be found in brackets):

- Start Delimiter (1B) beginning of a telegram, it determines the basic type of telegram (request, response with variable data length, response with fixed data length, token and no SD).

- Data Length (1B) the number of bytes between DA (Destination Address) and the end of DU (Data Units). Usually, the DU size is up to 32 bytes although the protocol allows to use up to 244 bytes.

- Repeated Data Length (1B) Data Length field repeated for protection.

- Destination Address (1B) valid addresses are in range of 0-127 (0x0 0x7F). Special cases are the address 126, which is reserved for commisioning and the address 127, which is reserved for broadcast. The most significant bit is used as an indicator for the inclusion of the DSAP and SSAP (see below).

- Source Address (1B) the same situation as DA except the address of 127. When a message is being broadcasted, there is no response and therefore the source address cannot be 127.

- Function Code (1B) it specifies the type of telegram, type of station, priority and telegram acknowledgment.

- Destination Service Access Point (1B) it specifies which services should be performed (for example read inputs, read outputs, read diagnostics, check configuration, etc.). It is used only if the MSB of Address is set.

- Source Service Access Point (1B) the same situation as DSAP applies here.

- Data Units (1B 244B) data to be sent to the device on the Destination Address.

- Frame Checking Sequence (1B) the checksum of the whole telegram.

- End Delimiter (1B) the fixed value of 0x16 indicates End Delimiter and therefore also the end of the frame. [14]

The communication using SRD transfer type is captured in the figure 3.

Figure 3: Example of Profibus communication [14]

# 3 Profibus Analyzer device overview

Profibus Analyzer will be an internal device of the Siemens company, which is currently being developed in Corporate Technology (R&D) department in Prague.

The list of planned properties:

• Input for two Profibus DP channels (9,6 kbps – 12 Mbps).

- Input for single Profibus PA channel (31,25 kbps).

- Three input triggers.

- Three output triggers.

- Ethernet interface.

#### 3.1 Hardware

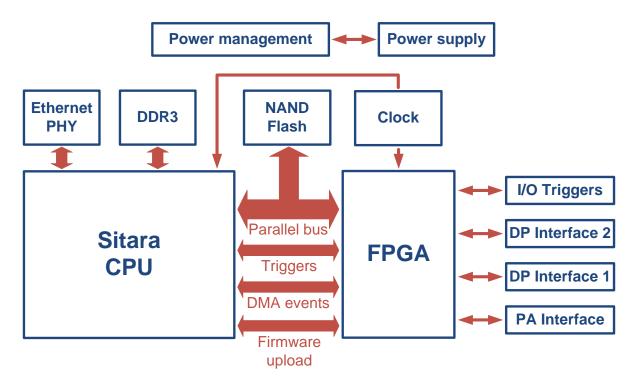

Figure 4: Block schematic

The core of the hardware is a Sitara CPU made by Texas Instruments, which is connected to the FPGA Cyclone IV. Profibus channels are connected via isolators to the FPGA, which will take care of adding timestamps and then of message forwarding to the CPU via the parallel communication interface. Finally, the communication between the CPU and the control PC running the control software is performed via the Ethernet interface.

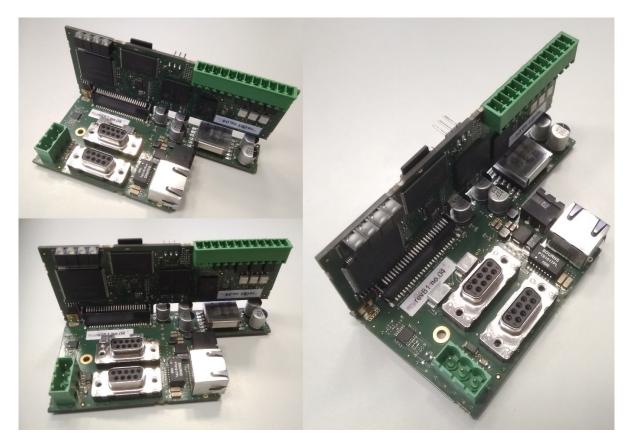

Figure 5: Profibus Analyzer hardware

#### 3.1.1 Sitara processor

The CPU AM3352 (that belongs to Sitara Processors family) was chosen to improve the performance of the board. It has all necessary features including the DMA, the memory controller and the higher clock frequency (up to 800 MHz). [10]

The list of main features of CPU AM3352 used in this work:

- GPMC General Purpose Memory Controller is used to access the FPGA, which is connected to the address and the data bus of the CPU and acts as a dynamic memory. The parallel memory interface is used so the communication bandwidth between the CPU and the FPGA is increased significantly (compared to the previous version of Profibus Analyzer, which used 2x SPI, the memory interface should be 8 times faster).

- EDMA Enhanced Direct Memory Access saves time of the CPU, because it takes care about memory transfers with just a minimal effort of the computing unit. In our case, it transfers data from the FPGA (via GPMC) to the DDR3 automatically using DMA transfer trigger pins that are used by the FPGA to trigger the DMA transfer whenever the data are ready at the FPGA side.

- EMIF External Memory Interface is used to connect the DDR3 memory to the CPU. The DDR3 is used to store runtime data and Profibus telegrams. For storing static data as Linux filesystem and kernel, the flash memory will be also connected.

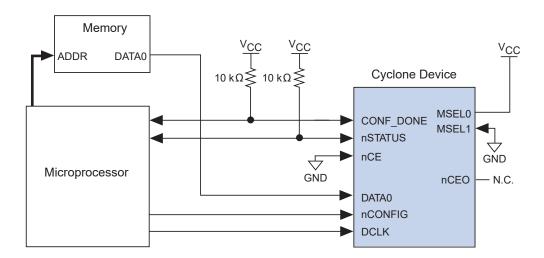

- SPI Serial Peripheral Interface is used to load the bitstream to the FPGA using the Passive Serial Programming mode (it will be described later in the Section 7.3).

- Ethernet MAC Ethernet is used to send data to the control PC.

- UART Universal Asynchronous Receiver-Transmitter is used for the Linux console to be accessible using the PC terminal.

- GPIO General Purpose Input Output pins are used for several purposes for changing the LED state (for example the heartbeat of the Linux kernel) and to control signals for the bitstream loading to the FPGA.

## 3.2 Software

The software part of the Profibus Analyzer can be divided into four categories:

- Operating system Standard RT-Linux kernel for Sitara processor, which is distributed by Texas Instruments company in version V4.9.28 will be used. Board-specific and Core-specific files of kernel will be rewritten to be compatible with the Profibus Analyzer hardware. The Profibus driver is added as a platform driver.

- Profibus kernel driver FPGA designed for receiving bytes from the Profibus network adds timestamps and sends internal telegrams, which contain received Profibus telegrams, to the CPU.

- Profibus Linux application The POSIX-compliant application, which is cooperating with kernel drivers via standard read/write mechanisms. The base behavior of the application is the interconnection of the Profibus driver and the TCP/IP stack to transfer all captured telegrams to the PC application.

- PC application GUI application that displays information about all telegrams received from the Sitara in a clear, readable and user-friendly GUI.

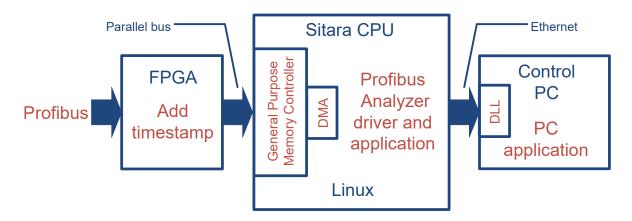

Figure 6: Software diagram

In the figure 6 the connection between separated software parts is clearly presented. Every piece of software is being developed separately.

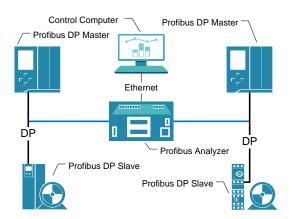

#### 3.3 Profibus Analyzer use cases

In this section, the use cases of Profibus Analyzer are presented. As mentioned in the Section 1, the main goal is the analysis of Slave redundant Profibus, but there are of course more use cases than this. All cases that are listed below can be extended by using input/output triggers. Using the input triggers, the measurement can start at the proper moment - for example exactly at the same time when the reset signal to the device is deactivated. Output triggers can be used for example to assert

the reset signal of the device or, in case it is connected to the interrupt input pin of the device, it can cause the interrupt.

List of standard use cases:

- The analysis of functionality of Profibus devices such as repeaters. Profibus Analyzer can be connected to the line in front of the repeater and to the line behind the repeater. Therefore it can be analyzed if the repeater works as expected.

- Replacing the repeater from the previous use case with another device, which has some internal logic, the delay between incoming and outcoming telegrams can be precisely computed.

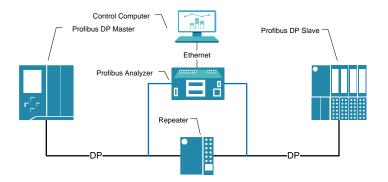

Figure 7: Use case: repeater analysis

• It is possible to analyze two different Profibus networks using a single device. The other benefit is that we get the timing information so we can analyze the synchronicity of these networks.

Figure 8: Use case: simultaneous analysis of two networks

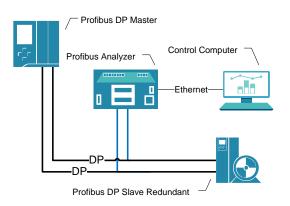

• Profibus Analyzer makes it possible to analyse the whole redundant communication in one time domain, which is the main feature and literally a reason, why the development was initialized. Differences in timing can be easily find out, so the debugging of such a network will be much more comfortable. The analysis of redundant communication using two independent devices is a challenging task and it is almost impossible to get really reliable results without our device.

Figure 9: Use case: redundant communication

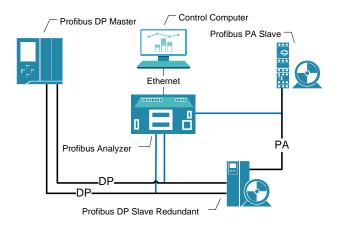

- It is possible to analyze not just the whole redundant communication, but also another PA channel in one time domain. It uses all of the mentioned benefits from the previous case, but moreover the additional PA channel can be analyzed there and therefore for example the delay of a device, which receives data from redundant DP channel and then transmit another data via PA channel, can be estimated.

- Because the DP and PA channels can be analyzed simultaneously, it is also possible to analyze the functionality of DP/PA coupler device (a device that creates a bridge between DP and PA channels and makes them compatible).

Figure 10: Use case: redundant communication with PA channel

# 4 Linux

In this chapter, the basics about Linux and Linux kernel are described. There is also a short history overview, the introduction to the Real Time systems and to the Real Time patch respectively.

## 4.1 Introduction

Linux is an open source Unix-like operating system based on Linux kernel developed under a license of GPLv2.

The most important features of Linux [5]:

- Unix-like type of operating system, which for example means that it is, or should be, kept as simple as possible and basic configurations and system files are saved as plain text (ASCII) files.

- It provides the support for

- multiprocessing

- multiprocessor architectures (wide support for different processors from different manufacturer)

- -32/64 bit architectures

- multi-user environment

- Preemptive OS the process cannot block processor for itself.

- Quickly spreading to all areas from the classical personal computers to the embedded systems.

- A large number of developers and therefore good support.

## 4.2 History

The first version of Linux kernel was developed by Finnish developer Linus Torvalds in 1991. The operating system was published on 17th September and Torvalds immediately started to get a lot of responses by mail, so he decided to keep developing the source code and publish new versions. During the next years, thousands of developers have started to work with Linux and therefore it spread all over the world. Originally, the Linux kernel was written for the i386 processor architecture, but during the time it was ported to many other platforms such as the ARM, the MIPS, the Atmel and so on.

The name Linux was chosen by the administrator of the FTP server, where the first version was published. Linus Torvalds wanted to name his operating system "Freax" as a connection of words free, freak and Unix, but the administrator Ari Lemmke did not like it, so he chose Linux as a connection of the name Linus and Unix.  $^1$

In the figure 11, there is a logo of Linux - a penguin called Tux. Tux was created by American programmer Larry Edwing in 1996. [6]

<sup>&</sup>lt;sup>1</sup>Just note here, that Linus did not like this version, because it seems too self-centered to him.

Figure 11: Linux logo

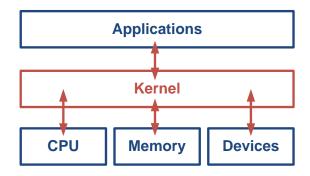

#### 4.3 Kernel architecture

The Linux kernel is a monolithic Unix-like operating system kernel which supports the loading of extensions (kernel modules). This architecture was chosen to keep the kernel more stable and maintainable. Linux operating systems are based on the Linux kernel and extended by custom modules.

The Linux kernel supports the preemptive multitasking (more application can run there simultaneously), the virtual memory (paging, each process has its own memory space), the memory management (the memory is managed only by the kernel, not by userspace applications), kernel modules/drivers and networking. Kernel modules (usually for new hardware support) can be dynamically loaded/unloaded from the kernel while the system is running.

There are two separated parts of the virtual memory (which define different levels/protection rings of privileges) - the kernel space (ring 0) and the userspace. This method provides the memory protection - the user space application (the application software and some drivers) cannot make inappropriate access to the memory (only to its own memory space) so it cannot corrupt any other process. On the other hand, from the kernel space, which is strictly reserved for the kernel, any memory is accessible, including hardware peripheral registers. [5]

Figure 12: Operating system kernel

#### 4.4 Real Time Preemptible Patch

When the Linux is used in real-time embedded systems, it is usually the Linux with RT-Preempt patch, which can guarantee the determinism of the system. Before the Linux RT Patch is described, it is important to define some basic properties of real-time operating systems.

#### 4.4.1 Real-Time Operating System (RTOS)

The main difference between a classical operating system and a real-time operating system is that the real-time operating system is deterministic. For example, in the classical operating system, it is possible that the GUI sometimes freezes as the processor is busy with other operations, but this has no fatal consequences. On the other hand, when the industrial robot moves from its operational space, it has to be immediately detected and act to prevent any damages or harms and it is not acceptable to wait for some computation to be done first. Therefore, real-time operating systems shall be used to guarantee quick responses. However, "Real Time" does not mean a fast computation, but it means quick responses with minimal delays to important events (a guarantee of worst-case times, deadlines, determinism). [7]

To achieve this, several features are introduced in the kernel of operating systems. It is for example the special scheduler for RT tasks (for example the Rate monotonic scheduler or the Earliest deadline first scheduler) which ensures meeting the deadlines and the preemptible kernel.

Real-Time operating systems can be divided into two groups according to the deadline type:

- Hard RTOS All deadlines have to be met under all circumstances, otherwise the consequences are catastrophic, for example the controller in a plane. An interesting thing is that the analysis of the behavior of this kind of the RTOS is much more easier than in the second case.

- Soft RTOS majority of deadlines have to be met, but some deadlines can be occasionally missed and the consequences will not be so catastrophic. But it is really tricky to define the term "occasionally" correctly. It has to be done from case to case.

#### 4.4.2 Real-Time Preempt Patch for Linux kernel

A real-time solution for the Linux kernel is called RT-preempt patch. The advantage is that the user-space application does not care whether it runs on a pure Linux or a Linux with the RT-preempt patch installed, but the real-time behavior is better in every case. [8]

The list of features included in this patch:

- Locking primitives inside the kernel are made preemptible.

- Critical sections inside the kernel (for example a spinlock protection) are preemptible, but non-preemptible critical sections are still possible (using a raw spinlock).

- The implementation of the priority inheritance for spinlocks and semaphores inside the kernel.

- Interrupt handlers are made preemptible each handler is now running in the preemptible kernel thread.

- Change of Timer API introducing high-resolution kernel timers and a separate timer for timeouts.

## 4.5 Kernel module and device tree basics

In this chapter basic information about kernel modules and a device tree are mentioned, because this knowledge is important to understand following sections (the Section 6 in particular).

#### 4.5.1 Kernel module

The kernel module is an extension of the kernel itself, which can be loaded during the booting time (like a driver) or on demand when the Linux is running (without a reboot). This is a great way of having the customized kernel without any great effort (for example remove unnecessary modules to reduce the size of kernel). Another advantage of the kernel modules is that the operating system's kernel does not have to be a monolithic piece of code which would lead to hardly maintainable code. New drivers and modules would have to be hardcoded to the kernel source code and therefore it would

make it too large. Thanks to modules, the kernel is just a reasonable-sized piece of code which can be extended. [13]

The code of the kernel module has to be implemented in a standardized way to ensure the portability among different versions of the kernel. All kernel modules have to include the file linux/module.h and implement initialization and exit functions, this is mandatory. These functions are called by the kernel using macros *module\_init* and *module\_exit* (contained in linux/init.h) when the kernel module is loaded/unloaded to/from the system. It ensures the initialization and deinitialization of necessary resources for the module.

When the kernel module is successfully loaded, some interface usually has to be implemented to communicate with the user-space application. This can be easily done by implementing file operation functions (and then fill struct file\_operations which can be found in the linux/fs.h) that include for example open, close, read, write and IOCTL functions. To be able to call any file operation function, it is necessary to have a file which is assigned to the kernel module. This file can be created either by the user using the command line or by the kernel module itself, which is a preferred way (for example node in the /dev/ directory).

When we talk about the platform device driver (which means the driver of some hardware that can be found in the device tree), it has to implement some additional functions like a probe and remove functions (filled to the struct platform\_driver) contained in a linux/platform\_device.h altogether with a definition of a table which contains compatible strings for device tree parsing (see the paragraph below for the explanation).

#### 4.5.2 Device tree

The device tree is a data structure which describes the devices present in the system (which includes the processor peripherals as well as the external hardware connected to the processor). By parsing this structure, the Linux kernel knows for example how much memory it has, where the modules like DMA or SPI are located, which of them shall be enabled and what driver shall be used to control them. As the name suggests, the structure is represented by a tree (in the memory it is represented by a tree of linked lists). Each node has a list of properties of several types like a string, signed/unsigned integer or array.

After a new device node is added to the device tree, the compatible string property usually has to be placed here to inform the kernel which driver should be used when the node is discovered. Other properties are filled according to device driver needs, which can be found in the documentation or directly in the code of the driver.

# 5 Linux installation on Profibus Analyzer hardware

As mentioned before, the RT-Linux will run on the Profibus Analyzer. The reason for using Linux for the embedded development is to make a comfort for the developer - using a stable system with the clearly defined API, portable and hardware independent code, using networking, multithreading and memory management. To take advantage of using the Linux for embedded platforms, a Processor SDK (Processor Software Development Kit) is provided to support plenty of platforms.

## 5.1 Processor SDK

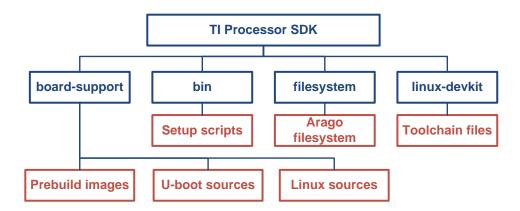

Texas Instruments provide their own Processor SDK, which contains not just a typical BSP (Board Support Package) with a bootloader, the Linux kernel and a filesystem to be able to create the whole system from the scratch, but also pre-build images for the Sitara processor family and examples to speed up the development and start using Linux on Sitara immediately.

The processor SDK contains (see also the figure 13 below the list):

- U-boot source codes (and its configuration files).

- Linux kernel source codes (and its configuration files).

- Linaro toolchain for cross-compiling.

- Scripts for the automation, for example the booting SD Card creation and other tasks.

- Documentation.

Figure 13: SDK containment overview

Although there is the support for Sitara processors, a lot of work still has to be done because of the hardware customization. The SDK is written to support TI hardware platforms (EVMs - Evaluation Modules), but if there is for example another DDR3 memory connected, it is necessary to update its timing in the U-boot or if the UART console pins are desired to be in another place (pins) it is necessary to change UART configuration.

#### 5.2 Booting procedure

To understand the complexity of a porting procedure, it is necessary to know what exactly is happening after the device is powered up - from loading the operating system image to the memory to the peripheral initialization.

The booting of the Sitara processor includes four steps - a primary bootloader, a secondary bootloader, an U-boot and a kernel boot. Each step (except for the primary bootloader, which is hardcoded in a factory) has a potential impact when the code is ported to another platform.

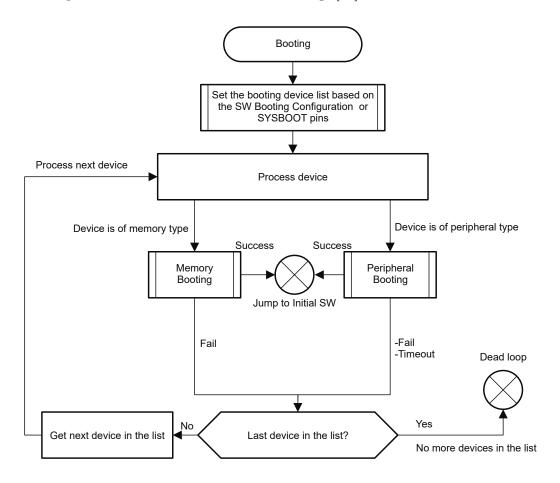

#### 5.2.1 ROM (primary) bootloader

The first phase of the booting procedure strongly depends on a type of processor. In case of the Sitara processor family, there is an option to select the boot mode by the configuration of strapping pins (called SYSBOOT [15:0]). It is possible to configure the initial crystal frequency, specify the source of an image (in our case SYSBOOT[4:0] pins are hardwired to sequence 0b10011, which gives the source boot sequence NAND (if not found continue to the next source) -> NANDI2C (not supported by hardware, certainly not found) -> MMC0 (preferred way of boot) -> UART0), enable/disable CLKOUT1 and specify options for NAND booting etc.

The Sitara ROM bootloader behavior is described in the figure 14. The code reads SYSBOOT pins, follows the sequence of source devices and tries them one by one until it reaches the end of the device

list. If the image is found in the device, then the code is loaded into the memory and the processor jumps to the initial address. If the image is not found in any device from the list, the software jumps to the infinite loop and waits for reset from the Watchdog. [10]

Figure 14: Sitara ROM boot code [10]

## 5.2.2 Secondary bootloader

When the device is found and the ROM boot code is ready to copy data to the processor RAM, we face a small problem - the size of the internal RAM is only 128kB (in fact it is a little smaller for the usage due to 18kB of the ROM code at the end of the memory and a secured first 1kB of the memory - it leaves exactly 109kB of the memory), but the U-boot code is quite complex and it does not fit (for example the prebuild U-boot image in SDK has 632 kB). The solution is to use the two-stage U-boot design which implements the primary bootloader and the final U-boot in separated binaries (therefore two stages of booting process).

The first generated binary is called MLO (minimal loader), SPL (secondary program loader) or sometimes an x-loader. The purpose is to initialize necessary peripherals (clocks, GPIO multiplexing, UART, GPMC and of course the setup of the DDR memory) to be able to copy the U-boot image to the RAM memory.

The second generated binary, which is generated at the same time as the SPL, is the U-boot image. Just note here that both binaries shared common source codes. [12]

#### 5.2.3 U-boot

The U-boot is the image of the monolithic code which performs necessary operations to successfully run the Linux kernel. It reads and stores (and optionally decompresses) the kernel image to the memory,

it performs the checksum to verify that the loading was successful and then it jumps to the entry point (the predefined address of the image header). When the SPL is not necessary, the U-boot is responsible for the environment setup to be able to load the kernel image to RAM. This setup includes the clock configuration, performing necessary pin mux settings (for example for the MMC) and timing configuration for the RAM (for example DDR3).

The U-boot contains its own command line, where various things can be set up. It is for instance the change of the name of the desired Linux kernel image (there can be more images in the source device memory), addresses where to load kernel image and the device tree, settings of output debug console and many other things. Some of these environment variables such as addresses are passed to the Linux kernel. [12]

#### 5.2.4 Kernel

When the Linux kernel starts, it performs the low-level system setup first. It initializes the virtual memory, installs interrupt handlers, starts the scheduler, decodes the device tree, loads kernel modules and finally sets up the user space context.

## 5.3 U-boot porting

List of actions which are usually needed in case of U-boot porting:

- Set Build Configuration by the modification of build configuration the interface used by U-boot is selected (for example GPMC, DDR) and the SPL usage is enabled or disabled.

- Set Pin Multiplexing pin multiplexing is related to the previous point, because the interface used by U-boot needs to have GPIOs configured in a proper way.

- Set Platform Data it contains information related to the custom hardware and which cannot be found automatically (for example DDR3 timing).

- Change Board level code this code performs necessary initialization of peripherals and interfaces using the Platform Data and it is used as the Board Adaptational Layer.

In this case, changes in U-Boot code were made because of the different DDR3 memory chip and because no card detection signal from the SD-Card is connected to the Sitara processor. Another minor changes were made in configuration files.

#### 5.3.1 Configuration

Most parts of the configuration for Profibus Analyzer were reused from the AM335x Evaluation Module. The difference is the specified Device tree which shall be used during the kernel boot. CONFIG\_SPL\_BUILD is defined to build both the SPL and the U-boot binaries.

The memory location for the FDT (Flattened Device Tree) was changed and the memory range was updated in arguments which are passed to the kernel from the U-boot because of the different size of the DDR3.

#### 5.3.2 Board init

Board specific source files were completely rewritten according to source files for the Beagle Bone Black. Source codes contain DDR3 settings, a configuration of initial LED state to signalize that the U-boot runs on the Sitara processor and a configuration of the Watchdog module to reset the Sitara in case of problem (in case of some initialization problem the program usually ends in a dead loop and therefore the Watchdog is really useful).

Pin multiplexing was also configured in the Board specific source files.

#### 5.3.3 Card Detect Signal

The special case for the Profibus Analyzer hardware is that the Card Detect signal is not connected from the SD-Card to the MMC module. Because of this, there was no other option than to rewrite few lines in the MMC driver to avoid checking this signal.

## 5.4 Linux kernel porting

List of actions which are usually needed in case of Linux kernel porting:

- Set Build Configuration by the modification of the build configuration the content of kernel is specified (for example which drivers will be available, debug modes, etc.).

- Update Device Tree by the modification of the device tree the developer tells the kernel what hardware is present and what driver shall be used.

In this case, changes in kernel source codes were made, as expected, in the device tree. Another part is, again, missing SD-Card Card Detect signal and configuration files.

#### 5.4.1 Configuration

The kernel build configuration was completely rewritten to make the kernel as small as possible, which means that only drivers which are really needed were kept in the configuration. The debug features were used only during the development and for the final version they were disabled.

#### 5.4.2 Device tree

The device tree was updated to support only peripherals which are necessary for the Profibus Analyzer functionality. List of supported peripherals, which are contained in the customized device tree (this tree includes am33xx.dtsi, which adds necessary features of the AM33xx processor family like the EDMA, CPU, etc. and therefore are not included in customized device tree):

- UART for serial debug console,

- MMC for the SD card,

- SPI0 for the FPGA firmware upload,

- GPMC for the memory (FPGA) access,

- Ethernet subsystem (CPSW, MAC, MDIO),

- Linux heartbeat LED,

- DDR3 memory size definition.

The MMC node was configured so the driver knows, that there is no Card Detect signal and therefore it is not a problem anymore. The memory range was updated as well.

Profibus Analyzer channel nodes were also added to the customized device tree. This is described in a 6.2.4 subsection.

# 6 Profibus Analyzer driver

This chapter describes the crucial part of the thesis. This chapter goes in more detail to give the reader the whole picture of the driver functionality altogether with the usage of the driver from the user-space application.

The main idea is to have a driver as a kernel module running in the background to prepare the data for the user-space application which will forward the data to the PC application via the Ethernet interface. Driver will automatically read the data from the FPGA and transfer them to the DDR3 memory. After receiving some amount of data, the driver will inform the user-space application that the data are ready to be sent. The key feature is to make this part of the transfer stack as fast as possible.

## 6.1 Driver design

According to the device architecture, it was intended to implement driver based on a producer-consumer scheme. In this subsection, the design of the driver together with the interface which will be used from the user-space application is described. Also, to describe the design completely, the way of loading the driver to the kernel is introduced.

## 6.1.1 Initialization/deinitialization

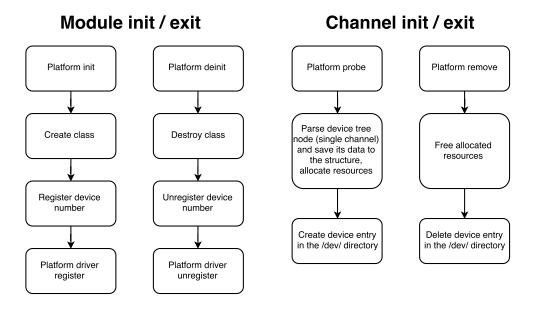

The description of the driver design should begin with the information how and when is the kernel module and the platform driver respectively inserted into the kernel.

First important thing is that the driver has to be installed in the booting memory. If the driver is successfully installed, the compatibility property string table is registered during the boot time altogether with the device number and class.

Whenever during the device tree parsing (during boot time) the compatibility string property is reached, the kernel finds the compatible driver by matching it with the compatibility string specified by the driver which was initialized before. Then the appropriate driver's probe function is invoked, the driver takes control and the device is initialized. The node in the /dev/ directory is usually created in this time.

This situation is captured in the figure below and it is divided into two parts:

- Module init/exit the part where the driver is loaded to the kernel. The class is created, the device number is registered and the compatibility string property is passed to the kernel.

- Channel init/exit the part where the device is found in the device tree and the device platform driver is chosen by the compatibility property. The driver then parses the device tree node and stores its data to the structure to be used later when the device is used. At the same time some of the resources are reserved, for example the memory is allocated for the cyclic DMA buffer. Each Profibus Analyzer channel has its own device tree node. This part is called separately for each node and therefore an entry in the /dev/ directory is created for every single channel.

Figure 15: Loading driver to the kernel

#### 6.1.2 Control interface

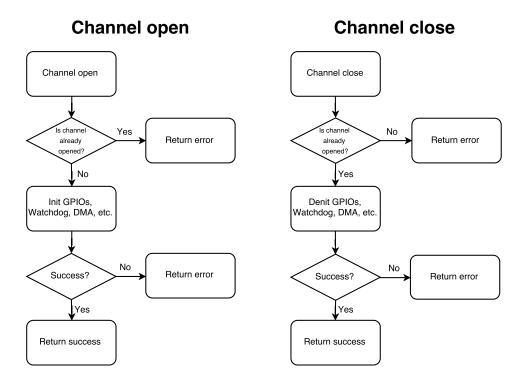

As mentioned before, each Profibus Analyzer channel has its own device tree node and therefore the channel init function is invoked multiple times, which means that there are different entries in the /dev/ directory for each channel. Therefore, the interface has to be designed to be used for each channel separately without affecting the others.

The preferred way of communication with the single channel is to use standard file operations, in our case, following functions are implemented:

- **Open** function is intended to initialize the single channel of Profibus Analyzer to be fully prepared to start capturing the data from the FPGA. The DMA channel is opened (but the transfer initialization is performed after the channel start function is called), the GPIO is exported and the appropriate interrupt is requested and the internal FIFO, which is used to hold the queue of the buffer information to be sent to the user space, is initialized.

- **Release** function is used to free the exported GPIO together with the requested interrupt. The internal FIFO is cleared, the Watchdog timer is deleted and the DMA channel is released.

Figure 16: Open close functionality

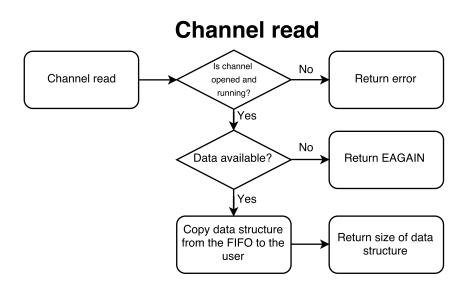

• **Read** function is designed to be as fast as possible. Therefore, just the information about the buffer (address and size packed in the structure) is passed from the driver to the user-space application. By using the shared memory concept between the driver and the application (using the mmap functionality), the user-space application can access the data from the driver. This approach was chosen to avoid the unnecessary memory copy from one buffer to another and therefore to avoid the CPU overload. The first structure in the internal FIFO is returned to the user. It is necessary to keep the order of used buffers. It prevents the situation that the buffer which was not read yet by the application is overwritten by the DMA.

Figure 17: Read functionality

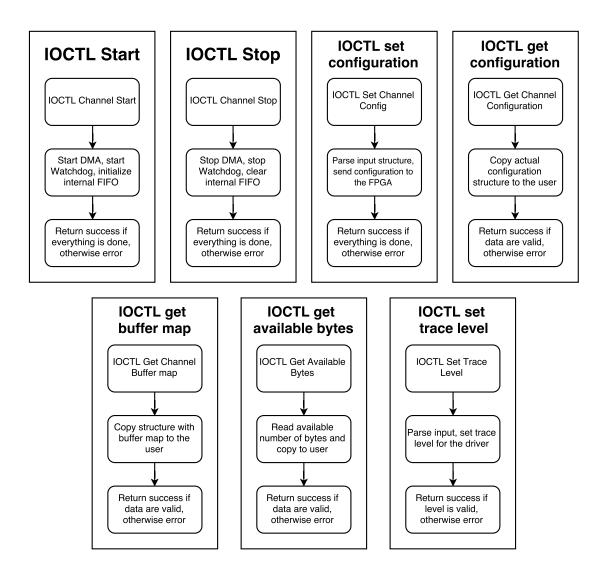

- Unlocked\_ioctl (Input Output Control) interface is used to send/receive commands to/from the driver. The following commands are used:

- Start is used to start capturing data from the Profibus channel.

- Stop is used to stop capturing data from the Profibus channel.

- Set configuration is used to configure FPGA settings such as Profibus channel speed.

- Get configuration is used to read current settings from the FPGA.

- Get buffer map is used to get buffer map, which was initialized during the device probing. The main idea is to pass buffer locations to the user-space application so it can be statically mapped before the channel is started. This approach saves a lot of time, because the mapping is time-consuming, and therefore just a single mapping at the beginning saves time and increases data throughput.

- Get available bytes is used to return the number of available bytes in the current buffer.

- Set the trace level (choose from debug/warning/error trace level).

Figure 18: IOCTL commands

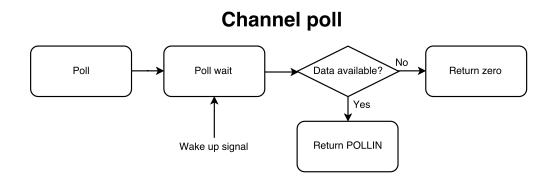

• **Poll** is implemented to support the *poll* and *select* functions, which can be used from the user-space application to check whether the data are available.

Figure 19: Poll functionality

### 6.1.3 Functionality

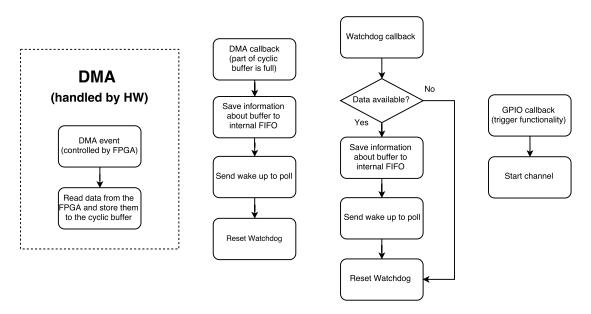

When the channel is configured and it is running, data should be transferred to the CPU memory automatically without any software support by using the DMA event trigger which is controlled by the FPGA chip. This is done by the appropriate configuration of the DMA controller, which will then transfer 8 bits on every trigger from the FPGA (the trigger comes as long as there are some data available in the FPGA's FIFO).

The DMA is also configured to cause interrupt after the buffer is full (DMA automatically switches buffers) and the handler is then responsible to signalize that there are some data available in the internal FIFO ready to transfer to the poll function (and through driver to the user-space application which is using the *poll/select* functions).

To avoid the situation when the data rate is really slow (for example some misbehavior on the bus) and the DMA interrupt occurs just occasionally which would then slow the transfer of the data to the PC application, the Watchdog timer was introduced. After some predefined time, the Watchdog interrupt occurs and buffers are checked for available data. If some data are available, they are placed to the internal FIFO, the signal is sent to the *poll* function and then the application has to take care about sending the data to the PC. The DMA callback always resets Watchdog counter to avoid unnecessary interference of the standard behavior.

The last supported functionality is handling the external trigger. This is done by installing the GPIO interrupt which is then responsible for starting the channel.

Just note here that described functionality is separated for every channel and therefore there are no shared resources among channels.

Driver behavior - channel is running

Figure 20: Diagram of driver behavior

### 6.2 Driver implementation

The implementation of the core features is described in this subsection. It is not worth to describe every detail, so the focus will be on the file structure, the interface to the user space and the DMA functionality, which unexpectedly required some additional features to be added.

### 6.2.1 Source code structure

It was decided to divide the functionality into more source files due to better readability, extensibility and maintenance of the source code. The source code is created by following files:

- C files

- profibus\_analyzer\_driver.c contains the mandatory functionality for the platform device driver like a file operations structure, platform driver operations and module init/exit functions.

- **profibus\_analyzer\_fcns.c** contains the whole functionality used for the data flow.

- Headers

- **profibus\_analyzer\_driver.h** contains the definition of the Profibus Analyzer structure which holds information about every single channel.

- profibus\_analyzer\_fcns.h contains only prototypes of the functions in complementary .c file.

- profibus\_analyzer\_ioctl.h contains the interface which is used to communicate with the user-space application.

#### 6.2.2 Data transfer functionality

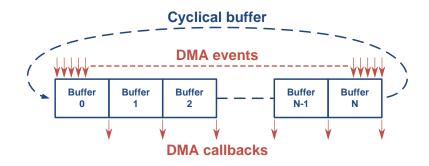

The most challenging part of the Profibus Analyzer driver implementation was to implement the data flow strategy which was described above (in the 6.1.3). The situation of the continuous data stream from the FPGA is captured in a figure 21.

Figure 21: Cyclical buffer with DMA callbacks

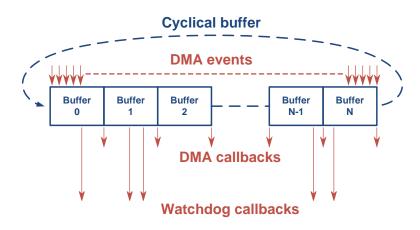

The DMA callback always appears before the Watchdog overflow and so only the buffer ID is necessary to determine the buffer correctly. As usual, nothing is perfect and therefore the driver has to deal with the situation of a non-continuous data stream from the FPGA. This situation is captured in the figure 22.

Figure 22: Cyclical buffer with DMA and WDG callbacks

The buffer is filled by the DMA, but the data rate is too slow. After some time, the Watchdog timer overflows and therefore the Watchdog callback is performed. Now, the driver has to find how many bytes have been transferred by the DMA transfer from the FPGA to the buffer (unfortunately, the DMA API does not provide such functionality and therefore it had to be implemented in a different way, which is described in the following section), it has to compute the buffer address and then put it in the internal FIFO.

As can be seen from the figure 22, because of the Watchdog callback, the buffer is no more aligned and callbacks which come after it have to deal with this situation by reading the previous source of data and then computing the buffer offset and size.

### Number of transferred bytes

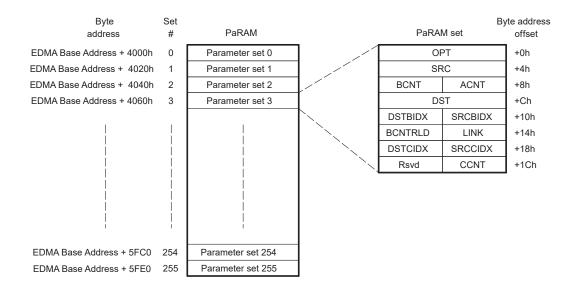

During the implementation of the driver, the function to read the number of transferred bytes had to be implemented because there is no support for this kind of action by the DMA driver. To implement this, the EDMA (Enhanced Direct Memory Access) controller area, which is present in the Sitara, had to be accessed directly by the driver.

The EDMA is a RAM-based architecture module, which in this case means, that the EDMA module contains a PaRAM (Parametrization RAM), where transfer parameters are stored. The PaRAM structure is captured in figure 23.

Figure 23: EDMA PaRAM[10]

As can be seen at figure 23, there are 256 sets in the RAM. Each PaRAM set is 32B and contains information needed by the single transfer. The most important is the BCNT field, where the remaining number of words can be found (for different configuration the CCNT and ACNT play important role as well). The cyclic DMA buffer is implemented as a cyclic chain of PaRAM sets (where last points to the first) and the currently active set is always copied in front of this chain.

Finally, the implementation was not so difficult. The PaRAM was mapped using the ioremap functionality, so the driver can access it. The copy of the PaRAM set is found during the channel start and the pointer to this PaRAM set is stored. The actual number of transferred bytes can be always determined by reading value from the PaRAM set (on a static address), because the actual set is always copied to this place. [10]

#### 6.2.3 Control interface to the user-space

Almost everything which is needed by the user-space application is contained in the IOCTL header. The header has to be the same for both, the driver and the user-space application.

#### Channel open/close

The channel open/close description can be found above. After the channel is opened, the descriptor is returned and then it can be passed to all the control functions like channel read and so on.

#### Buffer map

The buffer map structure is returned after the IOCTL command *IOCTL\_GET\_BUFFER\_MAP* is called. The purpose is to allow the user-application to map the buffers from the physical address to the

virtual address and therefore to allow the user-space application to access the driver buffers, because the mmap function takes some time and doing it after every read would not be comfortable and it would be slow.

The IOCTL command returns the structure (in the frame below), which contains following fields:

- *base\_addr* contains the physical address of the base of the cyclical buffer.

- *single\_buf\_size* holds the size of the single buffer.

- *number\_of\_bufs* holds the number of smaller single buffers in the cyclical buffer. Therefore the size of the cyclical buffer is the *single\_buf\_size* multiplied by the *number\_of\_bufs*.

```

typedef struct {

u32 base_addr;

ssize_t single_buf_size;

unsigned int number_of_bufs;

} p_a_buffer_map_t;

```

Figure 24: Structure which is returned from buffer map function

#### Channel read

The read function returns the structure (in the frame below), which contains following fields:

- *buffer\_id* contains the ID number of the buffer.

- *base\_addr* contains the physical address of the buffer. It is useful only when the buffer is not aligned, which happens only if the Watchdog interrupt occurred before.

- *size* holds the valid data size in the buffer (maximal value is the size of a single buffer).

- *align* is enum type which supports two values *e\_data\_aligned* and *e\_data\_misaligned*. The purpose of this field is to simply identify, whether the *buffer\_id* or the *base\_address* shall be used to locate the buffer.

- *source* is enum type which supports two values *e\_data\_source\_wdg* and *e\_data\_source\_dma*. The original usage was only for the debug, but at the end, it can signalize to the application that something is wrong, because the incoming data stream from the FPGA was interrupted.

```

typedef struct {

unsigned int buffer_id;

u32 base_addr;

ssize_t size;

t_p_a_data_alignment align;

t_p_a_data_source source;

} p_a_read_data_t;

```

Figure 25: Structure which is returned from the read function

#### Channel configuration

The configuration is set or get after the IOCTL command *IOCTL\_CHAN\_SET\_CONFIGURATION* or *IOCTL\_CHAN\_GET\_CONFIGURATION* is called. The purpose is to allow the user-application to configure the FPGA behavior.

The IOCTL command requires/returns the structure (in the frame below), which contains following fields:

• *speed* contains the speed of the Profibus Channel.

| <pre>typedef struct {</pre> |  |

|-----------------------------|--|

| int speed;                  |  |

| <pre>} p_a_config_t;</pre>  |  |

Figure 26: Structure holding the configuration of PFGA

### Channel input/output control

The rest of IOCTL commands are:

- IOCTL\_CHAN\_START/IOCTL\_CHAN\_STOP command starts/stops the channel.

- $IOCTL\_GET\_AVAILABLE\_BYTES$  returns the number of available bytes in the current single buffer.

- *IOCTL\_SET\_TRACE\_LEVEL* configures the trace level (possible levels are defined by enum as *p\_a\_trace\_level\_name*, where *name* can be debug, warning, error or none).

#### 6.2.4 Device tree

For every additional hardware there has to be a support in the device tree to make it work correctly. For the Profibus Analyzer, the GPMC and pin multiplexing settings have to be changed and Profibus Analyzer Channel nodes have to be added. These changes are described in this subsection.

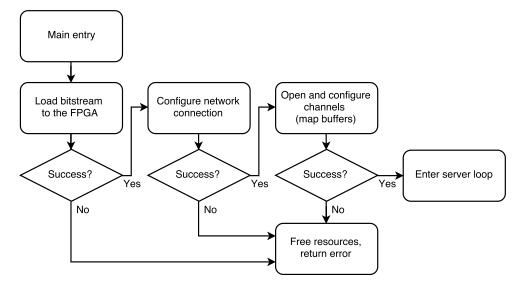

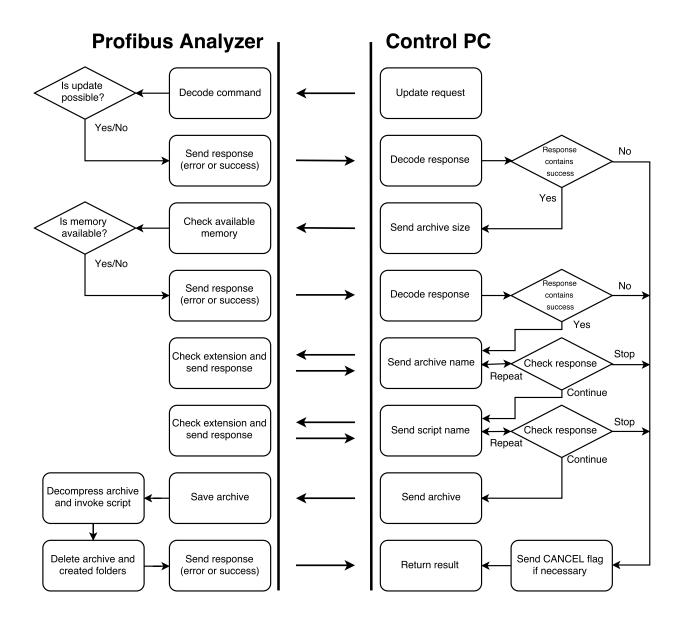

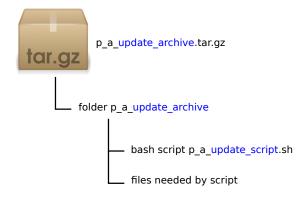

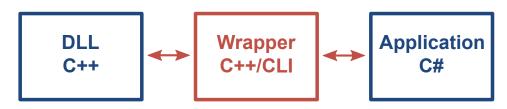

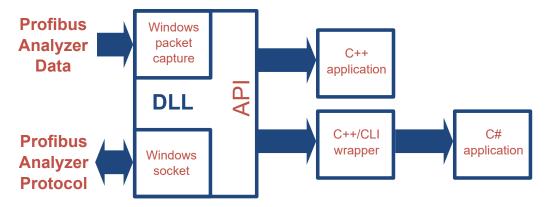

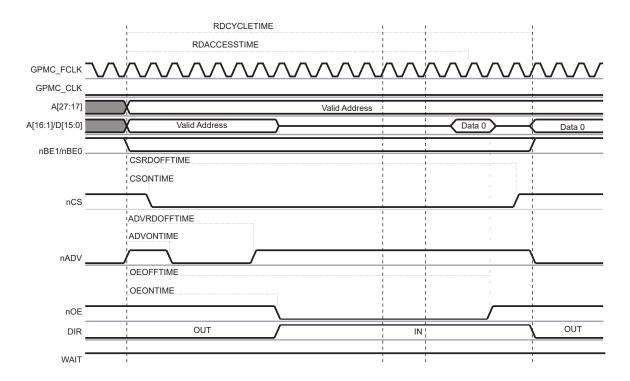

### General Purpose Memory Controller